CeCaS

Mannheim CeCaS is a supra-regional research project funded by the BMBF to develop a "Central Car Server" for future automated, connected and electrified vehicles. The project network consists of numerous industrial partners, accompanied by several academic research groups.

Overarching Objective: Automotive Supercomputing Platform - powerful Central Car Server concept based on new automotive qualified high performance processors, in FinFET supported by application specific accelerators and adaptive automotive SW stack for highly automated connected vehicles.

At the Technical University of Munich, three chairs (TUM-AIR, TUM-LIS, TUM-SEC) are involved in the CeCaS project network, contributing in the areas of model-based development, requirements management, software architecture, memory technology, and security.

Contribution of LIS

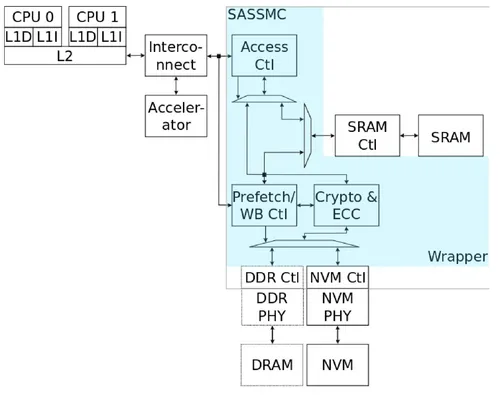

TUM-LIS is developing approaches for intelligent pre-fetching and write-back of data by the memory controller to increase the performance of the automotive processor. In addition, a prediction model for future addresses and data accesses is being investigated using machine learning methods such as reinforcement learning.

The current approach provides a wrapper layer around the DDR controller that realizes this functionality. It reduces the access latencies to external volatile and non-volatile main memories via adaptive prefetching of data and instructions in fast on-chip SRAM memories and by intelligent write-back of modified data located in the SRAM memory to the external main memory.

In the work on the wrapper layer we cooperate with TUM-SEC who investigate suitable lightweight techniques for transparent on-the-fly en-/de-cryption of data stored on external memory to prevent unauthorized access as well as error correction codes.

Workflow

In the CeCaS project we take a two-sided approach. On the one hand, we examine various implementation concepts and approaches with a SystemC based simulation model together with our partners. On the other hand, we are also working on an FPGA implementation, which offers a deeper level of abstraction for even more precise analyses. In both areas there are often topics for student work.

Involved Researchers

Open Student Work

Current Student Work

Development of a Hardware Test Framework for Simulation and FPGA-Based Evaluation

Beschreibung

Memory prefetching is a common technique used to hide memory access latencies and improve the performance of MPSoC architectures. In contrast to caches, data is read from the DRAM and stored in a fast on-chip buffer ahead of the actual CPU load request.

Such a memory prefetching mechanism is part of the TUM contribution to the CeCaS project and is currently under development. Besides a simulation environment, an FPGA-based prototype implementation was directly integrated into a State-of-the-Art MPSoC design.

The goal of this thesis is to develop a baremetal test environment for this preloading module to evaluate all possible testcases. The testenvironment will be developed in a hardware-related C programming style and can be executed directly on the FPGA prototype platform as well as on a cycle-accurate VHDL simulation.

Toward this goal, you will complete the following tasks:

1. Understanding the existing Memory Access and Preloading mechanism

2. Explore and understand possible corner-case scenarios

3. Develop a baremetal C program that triggers all corner cases

4. Analyse and discuss the results

Voraussetzungen

- Good Knowledge about MPSoCs

- Good C programming skills

- High motivation

- Self-responsible workstyle

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

FPGA-Based Design and Implementation of Dynamic Preloading Features

VHDL, C Programming, Distributed Memory, Data Migration, Task Migration, Hardware Accelerator

Beschreibung

Their main advantages are an easy design with only 1 Transistor per Bit and a high memory density make DRAM omnipresend in most computer architectures. However, DRAM accesses are rather slow and require a dedicated DRAM controller

that coordinates the read and write accesses to the DRAM as well as the refresh cycles. In order to reduce the DRAM access latency, memory prefetching is a common technique to access data prior to their actual usage. However, this requires sophisticated prediction algorithms in order to prefetch the right data at the right time.

The Goal of this thesis is to refine an existing DRAM preloading mechanism on an FPGA based prototype platform. It should be able to preload different pages alternatively and dynamically switch between two pages. This requires sophisticated changes in several components, FSMs and the Tag Memory of the hardware preload unit.

Towards this goal, you'll complete the following tasks:

1. Understanding the existing Memory Access and Preloading mechanism

2. VHDL implementation of the refined preloading functionalities

3. Write and execute small baremetal test programs

4. Analyse and discuss the performance results

Voraussetzungen

- Good Knowledge about MPSoCs

- Good VHDL skills

- Good C programming skills

- High motivation

- Self-responsible workstyle

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

A flexible Memory Preload & Security Extension for Multicore Architectues

Beschreibung

We are developing a dynamically configurable preload and crypto unit.

Specifically, this means two features: preload and/or dynamic activation/deactivation via software write AND self-adaptive burst length when the decryptor is disabled, otherwise fixed at 64B.

This requires, as discussed, routing the AXI ID to the memory controller, thus enabling stream separation of memory addresses (multicore aspect), and, on the other hand, providing a memory-mapped interface to the CPU.

We will then use this framework to further develop the priority mechanism.

This mechanism has two scientifically interesting features: separate prioritization for each core, arbitration between different cores, for example, based on access frequency, and possibly also externally configurable (e.g., one core is running a particularly important application, which is already determined in advance)

This allows to switch between a self-adaptive process and a user-configurable operation mode.

Optionally, you can also extrapolate additional pages and include them in the prioritization as well.

Voraussetzungen

- Strong Experience with VHDL Coding

- Basic Knowledge is C Programmng

- Basic knowledge on MPSoC, cache hierarchies etc.

- B.Sc. in Electrical Engineering or similar

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Integration of a Hardware Preload Unit into an AXI-based CVA6 Architecture

Beschreibung

Their main advantages are an easy design with only 1 Transistor per Bit and a high memory density make DRAM omnipresend in most computer architectures. However, DRAM accesses are rather slow and require a dedicated DRAM controller

that coordinates the read and write accesses to the DRAM as well as the refresh cycles. In order to reduce the DRAM access latency, memory prefetching is a common technique to access data prior to their actual usage. However, this requires sophisticated prediction algorithms in order to prefetch the right data at the right time.

The Goal of this thesis is to transfer an existing DRAM preloading mechanism to an FPGA based prototype platform of the RISC-V CVA6 architecture. This requires a profund understanding of AHB and AXI communication protocolls as well as the functionalities of the cache and memory hierarchie of an MPSoC system.

Towards this goal, you'll complete the following tasks:

1. Understanding the existing Memory Access and Preloading mechanism

2. VHDL implementation of the refined preloading functionalities

3. Write and execute small baremetal test programs

4. Analyse and discuss the performance results

Voraussetzungen

- Gutes Fachwissen über MPSoC Systeme

- Kenntnisse über Python-Programmierung

- Hohe Motivation

- Selbstverantwortliche Arbeitsweise

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Non-Intrusive Performance Monitoring Framework for a Memory Preloading Module

Beschreibung

A non-invasive performance monitoring module counter will be developed to evaluate memory prefetcher behavior at the last-level of cache. It will observe prefetch operations without altering system functionality or timing, ensuring accurate measurement of workload characteristics. Configurable counters will capture metrics like bandwidth usage, prefetch coverage, accuracy, and hit/miss ratios, in real time. The module will be implemented on an FPGA together with the rest of the system, and an available communication interface will be used to send the collected data to the attached PC. On the host side, a dedicated application will receive metric streams and update interactive dashboards, that will render live plots illustrating performance trends. Such visualization will facilitate intuitive analysis and real-time insights during live demonstrations under realistic workload conditions, and also help make future architectural decisions. The design of the module will keep in mind future expansion, leaving room for integration of additional performance metrics and advanced analysis capabilities. By combining hardware-based data collection with a flexible host application, the project will deliver a robust tool for cache prefetcher evaluation.

Voraussetzungen

- Strong Experience with VHDL Coding

- Basic Knowledge is C Programmng

- Basic knowledge on MPSoC, cache hierarchies etc.

- B.Sc. in Electrical Engineering or similar

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Completed Student Work

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de