6G-life

With research beginning on the next generation of mobile communications 6G, TUM joins forces with TU Dresden in the BMBF funded project 6G-life to develop new approaches regarding sustainability, security, resilience and latency in mobile communications.

Hereby, LIS is engaged in exploring new architectures and architecture extensions for network interface cards (NICs) in processing nodes. This is part of the chairs endeavor to investigate how much intelligence can be brought to the network interface, taking into account the specific needs of certain networking domains and applications.

Research Focus

Many 6G applications, such as extended reality (XR) or autonomous driving, will require low latency control loops to be closed over the network, thereby requiring processing near the user and decision-making early in the data path. This leads to a large increase in Edge Computing and a growing amount of differently dimensioned, heterogenous processing nodes. Since changing user and application behaviour can exert very volatile traffic characteristics and processing requirements, such processing nodes have to interact with the network adaptively and energy-efficiently, also to avoid overprovisioning single nodes.

Therefore, we at LIS want to explore how to extract information on current traffic characteristics and processing requirements in the NIC and how to use this information to efficiently provision the servers processing resources and reflexively react to changing conditions. More concretely, this involves:

- designing a packet processing architecture with the required logic to extract information from incoming traffic

- performing power management of the host CPU and its heterogenous resources

- making processing decisions early in the data path, reducing the load on the CPU

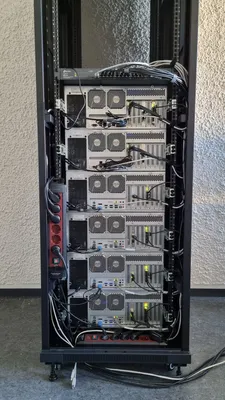

and much more. We are prototyping these contributions on FPGA-based NICs in a multi-server testbed at our chair.

6G Testbed

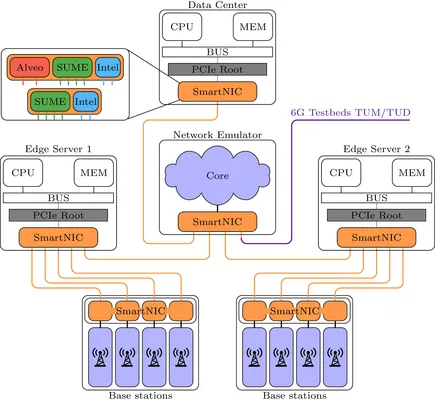

The LIS 6G Testbed and Demonstrator consists of 2 AMD Epyc Server nodes and 4 AMD Ryzen PC nodes, which are equipped with several Xilinx FPGAs (NetFPGA SUME and Alveo), as well as commercial Intel NICs. They are used for prototyping 6G-specific SmartNIC extensions, providing proof-of-concept evaluation and demonstration in a physical networking testbed. The nodes can be used in a variety of ways, depending on the specific use case and evaluation setup. The figure on the right shows an exemplary representation of the nodes in a typical 6G use case.

Student Work

Offered Topics

Are you interested in contributing to 6G-life? If you don't find an interesting topic listed here, sometimes there is also the possibility to define a topic matching your specific interests. If you have questions about the 6G-life project and student works at our chair, please contact Marco Liess.

Ongoing

SmartNIC-assisted Selective Data Distribution for Image Processing

Beschreibung

To improve the performance and energy efficiency of a

modern server, SmartNICs can be used to preprocess

incoming packets and gather characteristics on traffic

and processing requirements, as well as offer the possibility

to offload and accelerate specific functionalities. In the

context of Data Distribution in Vehicular Networks for

Automated Driving, an existing protocol and software

solution [1] offers the potential for SmartNIC-acceleration.

This state-of-the-art solution relies on selective data

distribution in a ROS2-environment to reduce the amount of

data transferred and thereby improve latency and efficiency.

While the offered software implementation already shows significant improvements, offloading certain protocol and packet processing to the SmartNIC promises much greater gains by avoiding expensive software loops and enabling hardware-accelerated processing.

The goal of this work is to implement the network protocol developed in [1] in FPGA-hardware, preferably using the P4 framework [2]. An existing implementation of the AMD Vitis Net P4 IP core can be used as a starting point. Further, the image processing can be offloaded to the SmartNIC and accelerated using parallel hardware and the onboard HBM on the SmartNIC's FPGA. This requires a custom RTL implementation of image format transformation and caching logic. The existing software implementation shall be used as a design reference and comparison in terms of performance evaluation.

[1] N. Sperling and R. Ernst, "Reducing Communication Cost and Latency in Autonomous Vehicles with Subscriber-centric Selective Data Distribution," 2024 IEEE 99th Vehicular Technology Conference (VTC2024-Spring), Singapore, Singapore, 2024, pp. 1-7

Voraussetzungen

- Programming skills in VHDL/Verilog, C and preferably P4 (and Python)

- Practical experience with FPGA Design and Implementation

- Good Knowledge of computer architecture, low-level software and OSI network model

- Comfortable with the Linux command line and bash

Kontakt

Marco Liess, M.Sc.

Tel.: +49.89.289.23873

Email: marco.liess@tum.de

Betreuer:

Linux Scheduler Implications for Load Balancing and Real-Time Networking

Beschreibung

With the advent of research on the next generation of mobile communications 6G, LIS is engaged in exploring architectures and architecture extensions for networking hardware, as well as improving the interaction between SmartNIC hardware, operating system, and application software. As 6G aims to support mission-critical applications, the demand for deterministic, real-time processing within network infrastructure has become paramount. The recent mainline integration of the real-time scheduler in Linux presents a unique opportunity to explore how operating system scheduling decisions directly impact networking performance in time-sensitive environments.

The incoming traffic load and with it the computing requirements on network processing nodes such as edge servers can span multiple magnitudes in a matter of milliseconds and less. This makes the task of load balancing and efficient scheduler decisions increasingly difficult, especially considering additional requirements like priority-awareness.

This thesis investigates the critical intersection of Linux scheduling policies and real-time networking performance. The research goals of this thesis include:

- Evaluating the performance implications of different Linux scheduling policies on networking performance

- Analyzing how scheduling decisions affect deterministic behavior in time-sensitive networking applications

- Assessing efficient load balancing mechanisms and the availability of priority-awareness for specific flows

- Identifying and potentially developing SmartNIC extensions to enhance Linux scheduling decisions

Voraussetzungen

- Good experience with Linux, Command Line Tools and Bash scripting

- Programming skills in C and Python

- Practical experience with the Linux Kernel, Kernel tracing functionality and low-level software

- Solid understanding of operating system concepts and hardware/software interactions

Kontakt

Marco Liess, M.Sc.

Tel.: +49.89.289.23873

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Linux Scheduler Implications for Load Balancing and Real-Time Networking

Beschreibung

With the advent of research on the next generation of mobile communications 6G, LIS is engaged in exploring architectures and architecture extensions for networking hardware, as well as improving the interaction between SmartNIC hardware, operating system, and application software. As 6G aims to support mission-critical applications, the demand for deterministic, real-time processing within network infrastructure has become paramount. The recent mainline integration of the real-time scheduler in Linux presents a unique opportunity to explore how operating system scheduling decisions directly impact networking performance in time-sensitive environments.

The incoming traffic load and with it the computing requirements on network processing nodes such as edge servers can span multiple magnitudes in a matter of milliseconds and less. This makes the task of load balancing and efficient scheduler decisions increasingly difficult, especially considering additional requirements like priority-awareness.

This thesis investigates the critical intersection of Linux scheduling policies and real-time networking performance. The research goals of this thesis include:

- Evaluating the performance implications of different Linux scheduling policies on networking performance

- Analyzing how scheduling decisions affect deterministic behavior in time-sensitive networking applications

- Assessing efficient load balancing mechanisms and the availability of priority-awareness for specific flows

- Identifying and potentially developing SmartNIC extensions to enhance Linux scheduling decisions

Voraussetzungen

- Good experience with Linux, Command Line Tools and Bash scripting

- Programming skills in C and Python

- Practical experience with the Linux Kernel, Kernel tracing functionality and low-level software

- Solid understanding of operating system concepts and hardware/software interactions

Kontakt

Marco Liess, M.Sc.

Tel.: +49.89.289.23873

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Linux Scheduler Implications for Load Balancing and Real-Time Networking

Beschreibung

With the advent of research on the next generation of mobile communications 6G, LIS is engaged in exploring architectures and architecture extensions for networking hardware, as well as improving the interaction between SmartNIC hardware, operating system, and application software. As 6G aims to support mission-critical applications, the demand for deterministic, real-time processing within network infrastructure has become paramount. The recent mainline integration of the real-time scheduler in Linux presents a unique opportunity to explore how operating system scheduling decisions directly impact networking performance in time-sensitive environments.

The incoming traffic load and with it the computing requirements on network processing nodes such as edge servers can span multiple magnitudes in a matter of milliseconds and less. This makes the task of load balancing and efficient scheduler decisions increasingly difficult, especially considering additional requirements like priority-awareness.

This thesis investigates the critical intersection of Linux scheduling policies and real-time networking performance. The research goals of this thesis include:

- Evaluating the performance implications of different Linux scheduling policies on networking performance

- Analyzing how scheduling decisions affect deterministic behavior in time-sensitive networking applications

- Assessing efficient load balancing mechanisms and the availability of priority-awareness for specific flows

- Identifying and potentially developing SmartNIC extensions to enhance Linux scheduling decisions

Voraussetzungen

- Good experience with Linux, Command Line Tools and Bash scripting

- Programming skills in C and Python

- Practical experience with the Linux Kernel, Kernel tracing functionality and low-level software

- Solid understanding of operating system concepts and hardware/software interactions

Kontakt

Marco Liess, M.Sc.

Tel.: +49.89.289.23873

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Completed

Kontakt

Betreuer:

Kontakt

Marco Liess, M. Sc.

Tel.: +49.89.289.23873

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Kontakt

Marco Liess, M. Sc.

Tel.: +49.89.289.23873

Email: marco.liess@tum.de

Betreuer:

Student

Kontakt

Marco Liess, M. Sc.

Tel.: +49.89.289.23873

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Betreuer:

Student

Kontakt

Marco Liess, M. Sc.

Tel.: +49.89.289.23873

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Kontakt

Marco Liess, M. Sc.

Tel.: +49.89.289.23873

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Student

Kontakt

Marco Liess, M. Sc.

Tel.: +49.89.289.23873

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Kontakt

Betreuer:

Kontakt

Marco Liess, M.Sc.

Tel.: +49.89.289.23873

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Kontakt

Betreuer:

Kontakt

Marco Liess, M.Sc.

Tel.: +49.89.289.23873

Gebäude: N1 (Theresienstr. 90)

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Kontakt

Marco Liess, M.Sc.

Technische Universität München

Lehrstuhl für Integrierte Systeme

Arcisstr. 21, 80333 München

Tel.: +49.89.289.23873

Raum: N2139

Email: marco.liess@tum.de

Betreuer:

Publications

- Reflex-enhanced Computing for Adaptive 6G Hardware. In: 6G-life: Unveiling the Future of Technological Sovereignty, Sustainability and Trustworthiness. Academic Press (1. Aufl.), 2026 mehr… BibTeX

- 6G Network Design and Operations. In: 6G-life: Unveiling the Future of Technological Sovereignty, Sustainability and Trustworthiness. Academic Press (1. Aufl.), 2026 mehr… BibTeX

- ecoNIC: SmartNIC-assisted power management for networking workloads in Linux servers. Microprocessors and Microsystems 105209, 2025 mehr… BibTeX Volltext ( DOI )

- Linux Power Management - Challenges in Modern Servers and how SmartNICs can help. ecoCompute Conference 2025, 2025 mehr… BibTeX

- Reflex-based Wire-rate Traffic Steering and Dynamic Service Relocation in Smart Edge Network Interface Cards (SENIC). International Conference on Mobile and Miniaturized Terahertz Systems (ICM2TS), 2025 mehr… BibTeX Volltext ( DOI )

- ecoNIC: Saving Energy through SmartNIC-based Load Balancing of Mixed-Critical Ethernet Traffic. 27th Euromicro Conference on Digital System Design (DSD) 2024, 2024 mehr… BibTeX Volltext ( DOI )

- X-MAPE: Extending 6G-connected Self-adaptive Systems with Reflexive Actions. 2023 IEEE Conference on Network Function Virtualization and Software Defined Networks (NFV-SDN), 2023 mehr… BibTeX Volltext ( DOI )