- 4/4Advanced Packet Segmentation and Buffering Algorithms in Network Processors. 4th International Conference on High Performance and Embedded Architectures and Compilers, 2009 mehr… BibTeX

- 3/4Improving Memory Subsystem Performance in Network Processors with Smart Packet Segmentation. Embedded Computer Systems: Architectures, Modeling, and Simulation, 20088th International Workshop, SAMOS mehr… BibTeX

- 2/4Buffer Allocation for Advanced Packet Segmentation in Network Processors. Application-Specific Systems, Architectures and Processors (ASAP), IEEE Press, 2008, 221-226 mehr… BibTeX Volltext ( DOI )

- 1/4Accelerating Packet Buffering and Administration in Network Processors. International Symposium on Integrated Circuits (ISIC), 2007 mehr… BibTeX

SmartMem

Background

Caused by steadily increasing throughput and flexibility requirements in the networking application domain, network processors have been introduced to provide a good compromise between performance and programmability. A network processor unit (NPU) is an ASIP optimized for packet processing that typically consist of several SW programable processing engines, specific accelerator modules, a memory subsystem for storing packets and network interfaces.

The Smartflow project, carried out together with Infineon Technologies AG, addresses the optimization of the ingress and egress data paths of access network processors with the focus on network interfaces and the memory management. SmrtMem, the TUM part of the project, focuses on memory management concepts of NPUs.

Goals

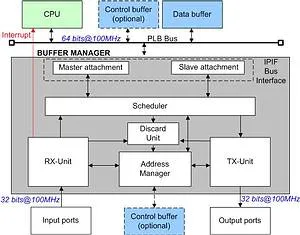

The main scope of SmartMem is the definiton of robust buffer management strategies that allow an increase of the NPU throughput while maintaining high memory efficiency and being feasible with limited architectural complexity. A basic principle of SmartMem is to completely offload the memory administrations tasks from the processing engines of the NPU and to implement them in a dedicated HW module (Buffer Manager) that autonomously stores and retrieves packets in/from the memory subsystem.

For the definition of an advanced Buffer Manager and a corresponding memory subsystem the following main aspects are currently being investigated:

- Data structures for storing variable sized packets in memory (packet segmentation, management of packet buffers with different segment sizes; control data structures for packet and queue administration).

- Memory architecture (memory types, internal/external memory) and mapping of data structures to memory modules.

- Influence of the interconnect infrastructure to access the different memory modules.

- Exploitation of specific properties of memory types and the memory organization considering the access patterns that are generated in NPUs.

Approach

Starting with a reference implementation of a conventional buffer management unit as part of an FPGA-based NPU platform, the requirements are analyzed and potential approaches are developed (the BM v1.0). New concepts are then validated with appropriate abstract system models that allow evaluating their benefits. Finally an enhanced memory manager is implemented in VHDL and integrated in the reference platform to demonstrate the viability of the approach.