- 5/5Benefits of Selective Packet Discard in Networks-on-Chip. Architecture and Code Optimization (TACO) Volume 9 (Issue 2), 2012, p. 1-21 mehr… BibTeX

- 4/5Hardware Support to Exploit Parallelism in Homogeneous and Heterogeneous Multi-Core Systems on Chip. Springer Verlag, 2010 mehr… BibTeX

- 3/5Comparison of Deadlock Recovery and Avoidance Mechanisms to approach Message dependent Deadlocks in on-chip Networks. The 4th ACM/IEEE International Symposium on Networks-on-Chip, 2010 mehr… BibTeX

- 2/5NoC Topology Exploration for Mobile Multimedia Applications. The 16th IEEE International Conference on Electronics, Circuits and Systems, 2009 mehr… BibTeX

- 1/5Hierarchical NoCs for Optimized Access to Shared Memory and IO Resources. Euromicro Conference on Digital System Design (DSD), 2009 mehr… BibTeX

RapidMPSoC - Rapid system prototyping and plattform-based design for mixed-signal multi-processor SoC: Future on-chip communication structures

Systems-on-chip (SoCs) are built of a steadily increasing number of components, like computation resources, memories, hardware accelerators, etc. Interconnecting this increasing number of components poses a problem to todays communication architectures (e.g. bus or crossbar switch), as they are lacking in scalability.

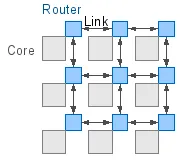

A new approach to this problem is the concept of network-on-chip (NoC), which can be viewed as the transfer of computer network principles to the on-chip world. However, a direct transfer of solutions from computer networks is not possible, since different constraints apply in the off- and on-chip world.

The main advantage of on-chip networks is their scalability, i.e. the aggregated link bandwidth of a network rises when additional cores are connected to the network. Nevertheless, on-chip networks also pose several challenges to the research community.The biggest challenge is the power/ performance problem: implementing a network with the required throughput for todays applications, leads to a network with way too high power consumption. Transfer latency is also an issue in networks, as it is relatively high compared to buses and it is not constant, but depends on the network's load. In addition to that, new technology generations are increasingly sensitive to the impact of low level effects like crosstalk on the actual performance and the reliability of the communication architecture.

Motivation and Targets

Target of this project is to provide NoC concepts that are better adapted to future SoC applications as well as the later realization on chip. The results of the investigation will be

- proposals of NoC architectures optimized for given application scenarios,

- guidelines for the selection of NoC topologies and the usage of specific link implementation techniques, based on a combined high level simulation approach considering analog effects,

- a collection of NoC building blocks to be used in the exploration of communication architectures on the system level abstraction layer.

Approach and Results

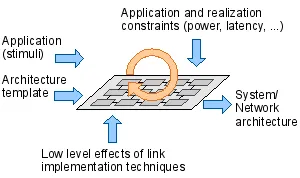

In order to find an optimized network for a given application, an architecture exploration is necessary. Such an exploration requires a high level simulation approach providing fast turn around times. However, we also want to consider analog effects on high speed communication links, because these low level effects are becoming more and more significant due to the ever shrinking feature size of integrated circuits. In RapidMPSoC we follow a combined approach that allows the exploration of high level network parameters as well as the consideration of low level link implementation techniques:

- High level network parameters include for example the network topology, the architecture of the routers, routing and forwarding schemes, etc. Hereby we want to lay emphasis on hierarchical network architectures with particular network topologies on the different hierarchical levels, adapted to the application requirements.

- Consideration of analog low level effects in the exploration, to allow a well-grounded decision on the use of specific link implementation techniques for the network. Examples of such techniques are low voltage swing links, serialization, asynchronous links, etc. In order to consider low level effects in the high level simulation model, we abstract and characterize these techniques.

The evaluation of NoCs will be done using the simulation model mentioned above and will also take into account other criteria like power and chip area.

A NoC simulator required for this project is developed at our institute.

Funding and Cooperations

RapidMPSoC is supported by the Bundesministerium für Bildung und Forschung (BMBF) and Infineon Technologies (IFX). Our project partners for the investigtation of future SoC interconnects within RapidMPSoC are Infineon Technologies and the Fraunhofer-Institut for Integrated Circuits, Department for Design Automation (FhG IIS EAS).