- 19/19Weighted Partitioning of Sequential Processing Chains for Dynamically Reconfigurable FPGAs. 23rd International Conference on Field Programmable Logic and Applications (FPL), 2013 mehr… BibTeX

- 18/19Partial Reconfiguration on FPGAs in Practice - Tools and Applications. Architecture of Computing Systems (ARCS), 2012 mehr… BibTeX

- 17/19A Prototypical In-Car Entertainment Setup Using Software Defined Radio and Ethernet/IP-based In-Vehicle Communication. The First International Conference on Advances in Vehicular Systems, Technologies and Applications (VEHICULAR), 2012 mehr… BibTeX

- 16/19Multi-Standard Processing using DAB and 802.11p on Software Defined Radio Platforms. 7th Karlsruhe Workshop on Software Radios (WSR), 2012 mehr… BibTeX

- 15/19On the Accuracy of sum-based Logic and Power Estimates in hardware-accelerated SDR systems. 7th Karlsruhe Workshop on Software Radios (WSR), 2012 mehr… BibTeX

- 14/19An Evaluation on Using GPU Coprocessing for Software Radios on a Low-cost Platform. Conference on Design & Architectures for Signal & Image Processing (DASIP), 2012 mehr… BibTeX

- 13/19Partitioning and Context Switching for a Reconfigurable FPGA-based DAB Receiver. Conference on Design & Architectures for Signal & Image Processing (DASIP), 2012 mehr… BibTeX

- 12/19Analytical Design Space Exploration based on statistically Refined Runtime and Logic Estimation for Software Defined Radios. Euromicro Conferences SEAA & DSD, 2012 mehr… BibTeX

- 11/19An Efficient DVB-T2 Decoding Accelerator by Time-Multiplexing FPGA Resources. 22nd International Conference on Field Programmable Logic and Applications (FPL), 2012, 75-82 mehr… BibTeX

- 10/19Partitioning and Context Switching for a Reconfigurable FPGA-based DAB Receiver. DASIP, 2012, 1-8 mehr… BibTeX

- 9/19An Optimized Software-defined Digital Audio Broadcasting (DAB) Receiver for x86 Platforms. 7th Karlsruhe Workshop on Software Radios (WSR), IEEE, 2012, 1-8 mehr… BibTeX

- 8/19Improving the Performance of Digital Radio Mondiale Plus (DRM+) by LDPC Channel Coding. IEEE International Symposium on Broadband Multimedia Systems and Broadcasting, 2011 mehr… BibTeX

- 7/19A modelbased software generation approach qualified for heterogeneous GPGPU-enabled platforms. International Conference on Parallel Computing (ParCo), 2011 mehr… BibTeX

- 6/19Real-Time Signal Processing on Low-Cost-FPGAs using Dynamic Partial Reconfiguration. International Symposium on Integrated Circuits, 2011 mehr… BibTeX

- 5/19Concept and Design of an SNR-adaptive DRM+/FM Receiver using Dynamic Partial Reconfiguration (DPR) of FPGAs. 11th Workshop Digital Broadcasting, 2010 mehr… BibTeX

- 4/19Energy consumption of Graphic Processing Units with respect to automotive use-cases. International Conference on Energy Aware Computing (ICEAC), 2010 mehr… BibTeX

- 3/19Implementation and Fine-grain partitioning of a DAB SDR receiver on an FPGA-DSP platform. 6th Karlsruhe Workshop on Software Radios (WSR), 2010 mehr… BibTeX

- 2/19Flexible multi-standard multi-channel system architecture for Software Defined Radio receiver. Intelligent Transport Systems Telecommunications (ITST), The 9th International Conference on ITS Telecommunications, 2009 mehr… BibTeX

- 1/19Resource-efficient Sequential Architecture for FPGA-based DAB Receiver. Workshop zu Software Radio WSR, 2008 mehr… BibTeX

PROTON - Software Defined Radio platform for automotive telematics applications

Overview

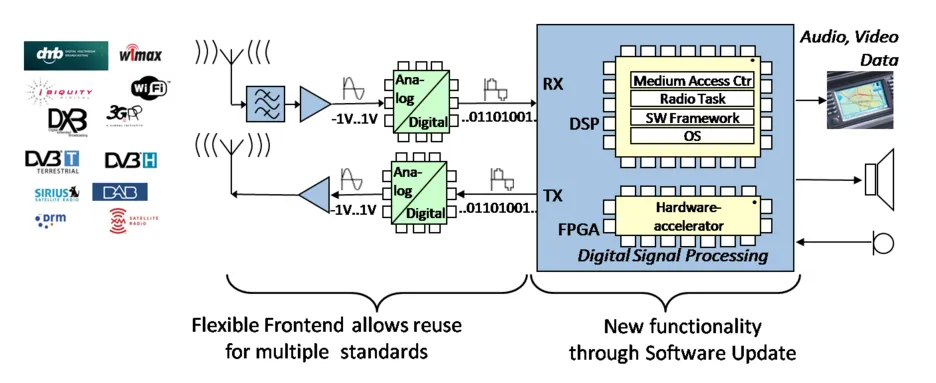

The number of different wireless standards is growing rapidly. Bringing current and future broadcast and communication into the vehicle allows car manufacturers to create new customer experience by providing entertainment and information.

Developing an separate electronic control unit (ECU) for each wireless standard takes a long time, which heavily delays the introduction of new systems and services.

By moving the signal processing from specialized SoCs to programmable hardware and processors, this system enables the integration new wireless standards through a firmware upgrade.

Research Focus

Early Design Space Exploration for SDR

For system architects, it is important to estimate the required processing power of the application scenario to determine a suitable architecture and select a suitable set of chip hardware.

We investigate ways to improve accuracy for early design estimations by considering estimation inaccuracies for both software and hardware accelerators based on tasks modeled as synchronous dataflow graphs.

Architectures for SDR

The required processing power for SDRs can come from FPGAs or DSPs. While DSPs have specialized set of instructions or vector operations that are suitable for a demodulation or channel correction, FPGAs offer a higher degree of freedom, for example to implement special channel decoders in hardware.

Dynamic Reconfiguration of FPGAs allows to expand the available resources on the FPGA by swapping hardware accelerators during system runtime. This increases logic utilization for otherwise idle hardware.

PROTON Project Website

More details on the PROTON/PLATA project and the contribution of partners can be found on http://www.proton-plata.fr/