- 6/6A TSV-Property-aware Synthesis Method for Application-Specific 3D-NoCs Design. Design Automation and Test in Europe (DATE), Friday Workshop on 3D Integration, 2014 mehr… BibTeX

- 5/6System Integration - The Bridge between More than Moore and More Moore Design. Design Automation and Test in Europe (DATE), Friday Workshop on 3D Integration, 2014 mehr… BibTeX

- 4/6Virtualized and Fault-Tolerant Inter-Layer-Links for 3D-ICs. Microprocessors and Microsystems Volume 37 (Issue 8), 2013, pp 823-835 mehr… BibTeX

- 3/6Networks-On-Chips für 3D-ICs. 7. ITG/GI/GMM-Fachtagung, 2013 mehr… BibTeX

- 2/6NEEDS - Nanoelektronik-Entwurf für 3D-Systeme. Zuverlässigkeit und Entwurf, 6. GMM/GI/ITG-Fachtagung (ZuE) , 2012 mehr… BibTeX

- 1/6TSV-Virtualization for Multi-Protocol-Interconnect in 3D-ICs. 15th EUROMICRO Conference on Digital System Design (DSD), 2012 mehr… BibTeX

NEEDS - Interconnection Networks for 3D-ICs

The project NEEDS explores the design of stacked chips in order to cope with the new requirements of information and communications systems by three dimensional integration of systems in the timeframe of 5 to 10 years. To reach theses goals, methods and tools from different design domains will be explored and integrated into a comprehensive design framework.

The overall objective is to find adequate analysis, exploration and synthesis methods for an optimized 3D integration with regard to the integration technologies in use. Design optimization in this context should be carried out in a holistic manner, i.e. considering a subtasks, and independent of the application domain.

Special focus is given to the optimization of costs and thus also on the assessment of costeffectiveness of 3D integration. As a project result, methods for 3D integration will be presented and demonstrated as a common development platform.

The project NEEDS is a cluster research project, that is carried out in close cooperation with multiple partners in Germany.

Research Focus

In our sub-project of NEEDS we are focused on research on the on-chip communication infrastructure for 3D-ICs.

Our main focus is on:

- Design of vertical links for 3D-ICs

- (semi-)automatic NoC generation for 3D-ICs

Vertical Links for 3D-ICs

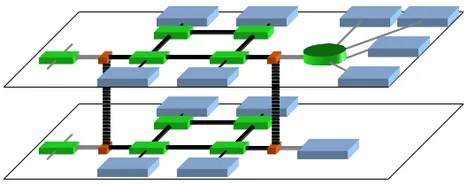

In our research we investigate and develop vertical hubs for 3D-ICs. Such vertical links are formed by arrays of Through Silicon Vias (TSVs). TSVs are very short interconnects with a low capactive load, however with a large area footprint.

Our main objectives are:

- Leverage TSV properties

- Reduce TSV count

- Allow migration from 2D to 3D designs

The main favorable property of TSVs is the low electric capacitance. This allows to run TSVs with a much faster clock, than the intra-layer-links. Therefore, to fully utilize a TSV-link several logical links are mapped on one TSV-link and are operated in a TDMA fashion. This reduces the TSV count and therofere leads to a reduced footprint. As the yield of 3D-ICs drops with a growing number of TSVs, reducing TSV count also improves the overall yield.

3D NoC Synthesis

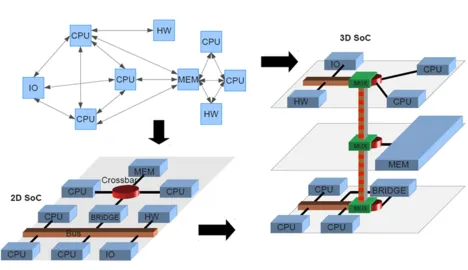

The basic idea is to (semi-)automatically build an 3D interconnection network based on a communication graph and a preliminary floorplan. A NoC-Generator tool is developed, that (semi-)autmatically constructs an optimizes the communication infrastructure for a 3D-IC.

The NoC-Generator iteratively optimizes the network and exchanges information with other tools developed in the NEEDS project, like an exploration tool, a floorplanner and a thermal analysis tool.

Two methods are investigated for generating the NoC:

- Direct generation of the 3D-Interconnection network, based on the communication dependencies in the communication graph and the annotated bandwith and latency requirements.

- Generation of an intermediate 2D communication network. Here, first a 2D network is constructed and later when the chip is "folded" to a 3D system, vertical hubs are inserted, that efficiently allow to continue the 2D-links to other chip layers.