- HW-Flow: A Multi-Abstraction Level HW-CNN Codesign Pruning Methodology. Leibniz Transactions on Embedded Systems (LITES), 2022 mehr… BibTeX

- AnaCoNGA: Analytical HW-CNN Co-design using Nested Genetic Algorithms. Design, Automation & Test in Europe Conference & Exhibition (DATE), 2022 mehr… BibTeX

- Accelerating and Pruning CNNs for Semantic Segmentation on FPGA. Design Automation Conference (DAC), 2022 mehr… BibTeX

- HW-FlowQ: A Multi-Abstraction Level HW-CNN Co-design Quantization Methodology. ACM Transactions on Embedded Computing Systems (TECS), 2021 mehr… BibTeX

- BinaryCoP: Binary Neural Network-based COVID-19 Face-Mask Wear and Positioning Predictor on Edge Devices. IEEE International Parallel & Distributed Processing Symposium, Reconfigurable Architectures Workshop (IPDPS-RAW), 2021 mehr… BibTeX

- Adversarial Robust Model Compression using In-Train Pruning. IEEE/CVF Conference on Computer Vision and Pattern Recognition Workshops (CVPRW), 2021 mehr… BibTeX

- Pruning CNNs for LiDAR-based Perception in Resource Constrained Environments. IEEE Intelligent Vehicles Symposium Workshops (IV Workshops), 2021 mehr… BibTeX

- Investigating Binary Neural Networks for Traffic Sign Detection and Recognition. IEEE Intelligent Vehicles Symposium (IV), 2021 mehr… BibTeX

- Hardware-Aware Mixed-Precision Neural Networks using In-Train Quantization. British Machine Vision Conference (BMVC), 2021 mehr… BibTeX

- Binary-LoRAX: Low-power and Runtime Adaptable XNOR Classifier for Semi-Autonomous Grasping with Prosthetic Hands. International Conference on Robotics and Automation (ICRA), 2021 mehr… BibTeX

- BreakingBED - Breaking Binary and Efficient Deep Neural Networks by Adversarial Attacks. Intelligent Systems Conference (IntelliSys), 2021 mehr… BibTeX

- OrthrusPE: Runtime Reconfigurable Processing Elements for Binary Neural Networks. 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), 2020 mehr… BibTeX

- L2PF - Learning to Prune Faster. International Conference on Computer Vision & Image Processing (CVIP), 2020 mehr… BibTeX

- Binary DAD-Net: Binarized Driveable Area Detection Network for Autonomous Driving. International Conference on Robotics and Automation (ICRA 2020), 2020 mehr… BibTeX

- ALF: Autoencoder-based Low-rank Filter-sharing for Efficient Convolutional Neural Networks. The Design Automation Conference (DAC), 2020 mehr… BibTeX

- An Efficient FPGA Accelerator Design for Optimized CNNs using OpenCL. ARCS Konferenz, 2019 mehr… BibTeX

- Resource-Aware Multicriterial Optimization of DNNs for Low-Cost Embedded Applications. Conference on Computer and Robot Vision, 2019 mehr… BibTeX

- DSC: Dense-Sparse Convolution for Vectorized Inference of Convolutional Neural Networks. Safe Artificial Intelligence for Automated Driving (SAIAD), 2019 mehr… BibTeX

MLOPs - Development, Optimization and Deployment of Machine Learning Algorithms on Embedded Hardware

Neuronale Netze sind in den vergangenen Jahren zum de facto Standard für eine Vielzahl von Bildverarbeitungsalgorithmen geworden. Allerdings wirft ihre Anwendung in eingebetteten Systemen wie beispielsweise dem autonomen Fahren oder der Robotik große Herausforderungen auf. Besonders die zielgerichtete Optimierung der Algorithmen hinsichtlich der Hardwareeffizienz, des Energiebedarfes bis hin zu kosten-optimierten Beschleunigern für die Edge-Inferenz von tiefen neuronalen Netzen ist ein spannendes Forschungsgebiet.

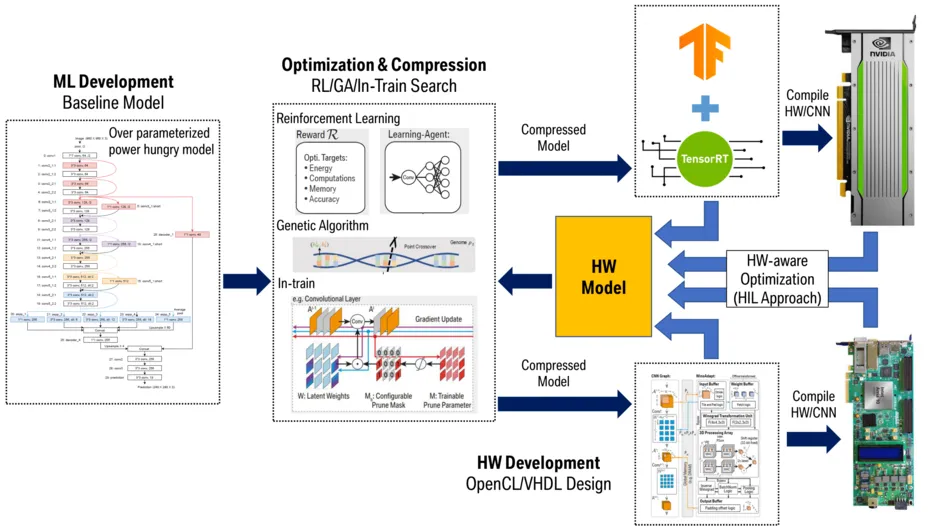

Unsere Forschungsgruppe beschäftigt sich mit dem HW/CNN Co-Design, also der Bestrebung, Designer der Algorithmen, Toolchain und Hardware Architekten gleichermaßen bei der Optimierung von lernbasierten Anwendungen einzubinden. Unabhängig ob einem Top-Down, Bottom-Up oder Meet-in-the-Middle Paradigma folgend, muss die Hardwarearchitektur die parallele Verarbeitung der beträchtlichen Anzahl von Faltungsoperationen unterstützen, geschickte Datenfluss- und Wiederverwendungsschemata von Eingangs-Aktivierungen, Parametern und Operanden gewählt werden und schlanke und komprimierte neuronale Netz Architekturen optimieret werden, die es ermöglichen, bereitgestellte HW Ressourcen zu nutzen.

Wir haben uns ganz darauf verschreiben, Methoden und Verfahren zu erforschen, die darauf abzielen, Machine Learning Modelle in echten eingebetteten Systemen zuverlässig und effizient bereitzustellen. MLOps stehen hierbei für uns im Fokus einer datengetriebenen Optimierung und Anwendung von neuronalen Netzen in eingebetteten Systemen. Willst auch du ein Teil der Veränderung sein, dann wirf einen Blick auf die unten ausgeschriebenen Seminar- und Abschlussarbeiten.