Bavarian Chip Design Center

The Bavarian Chip Design Center (BCDC) is a joint project between three Fraunhofer Institutes (AISEC, EMFT, and IIS) and five universities and colleges (FAU, HM, OTH, THN, and TUM), funded by the Bavarian Ministry of Economic Affairs, Regional Development and Energy. It aims to reduce the dependence on foreign semiconductor companies by supporting local chip design, production, and talent recruitment.

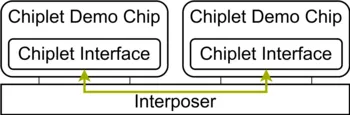

Its Chiplet Systems platform, as part of the Design Ecosystem subproject, follows the EU Chips Act's heterogeneous integration pilot line, investigating the development of chiplets, their interconnect, and applications that benefit from the special approach. Several TUM chairs (AI-Pro, CAPS, EDA, LIS, LSE, MNT, MSA, and SEC) collaborate on the design of a RISC-V-based chiplet demonstration chip for high-performance computing. Two of these chips will be connected via an interposer to simulate a system of interconnected chiplets.

At LIS, we work on a high-performance, low-latency chiplet interconnect with additional application-specific features managed by a smart protocol controller. It closes the gap between the physical layer developed at TUM-LSE and the system bus, connecting the contributions of other project partners. Our work is based on an existing standard, the Universal Chiplet Interconnect Express (UCIe). We extend it by a layer above its die-to-die adapter and protocol layers.

The addition layer is supposed to comprise some features beyond UCIe's default functionality. Example concepts are more advanced error detection and correction, transmission redundancy, adaptive lane utilization, and the integration of a secure element contributed by TUM-SEC, as shown in the graphic below. Exactly which additions will be implemented will become clear as the project progresses. Most of them are to be utilized selectively through the classifier sub-layer, deciding what features should be applied to data flows based on application requirements.

A prototype of the smart protocol controller will be developed in FPGA technology and a tapeout for the entire chiplet demonstration chip is planned.