Smart NIC Infrastructure

Extending the RISC-V Instruction Set for a SmartNIC Infrastructure (Tandem: Heilbronn + Garching)

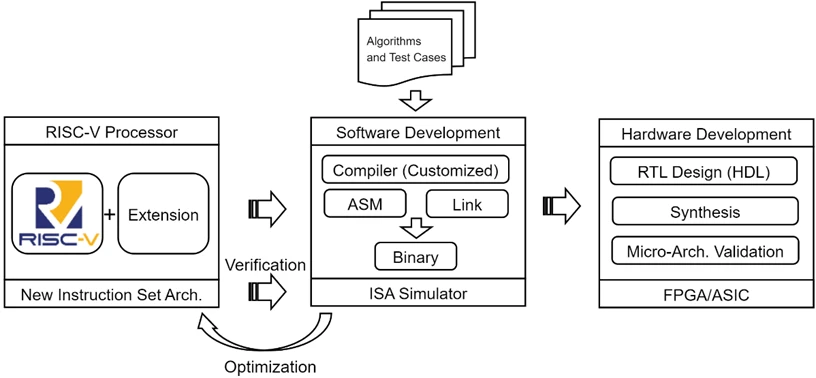

The project focuses on the augmentation of the Reduced Instruction Set Computer (RISC-V) instruction set architecture (ISA) to facilitate network data transfers between Network Interface Cards (NICs) and computational nodes. The primary aim is to mitigate host-system overhead by introducing ISA extensions that operate seamlessly at the cache and register level, analogous to DMA/RDMA functionalities. The project follows a collaborative approach:

- The team in Garching (CAPS) traces software prerequisites and frames the required software implementations.

- The team in Heilbronn (CAOS) will implement the precise extension of RISC-V ISA processor to accommodate the specified enhancements.

Both entities undergo experimental hardware simulation, implementation, and comprehensive evaluation of the newly introduced ISA extensions. This multifaceted collaboration combines software specification and hardware refinement expertise to advance the RISC-V architecture to applications in high-performance computing and efficient network communication between nodes in general.