Side-Channel Attacks and Countermeasures

Contact: Manuel Brosch, Matthias Probst, Jonas Schupp, Stefan Kögler

Side-channel analysis represents a major threat to the security of cryptographic embedded devices. By passively monitoring the activity of a device, side-channel information can be obtained, e.g. by measuring the variations of the electro-magnetic field over the chip surface or by obtaining power measurements. The information leaked by a device during the computation can be exploited using statistical analysis in so called side-channel attacks.

Over the last two decades, a varietey of side-channel attacks have been proposed. On the other hand, many implementation countermeasures have been proposed to thwart side-channel attacks. This quest for novel attacks and countermeasures is still a vivid research area. The main challenge in the field of secure implementations is to find the best trade-off between standard design constraints like speed, area and power consumption and physical security constraints like side-channel countermeasures.

The Chair for Security in Information Technology focusses on side-channel analysis and the development of countermeasures for Post-Quantum Cryptography and Neural Networks.

Side-channel analysis of neural network implementations is of growing importance as machine learning models are increasingly deployed on resource-constrained and security-critical hardware platforms. SCA exploits physical leakage, such as power consumption, electromagnetic emanations, or timing information, to infer internal computations or model parameters. For neural networks, such leakage can reveal sensitive information including weights, biases, or activation thresholds, effectively exposing proprietary architectures or confidential training data. This poses a significant threat to both intellectual property protection and data privacy, particularly in edge devices, embedded systems, and hardware accelerators where models are executed locally. Consequently, the systematic evaluation of neural hardware against side-channel vulnerabilities is essential to assess and enhance its resilience, inform the design of secure architectures, and develop countermeasures that preserve model confidentiality without compromising computational efficiency.

In the advent of Post-Quantum Cryptography, new cryptographic algorithms are proposed and deployed. It is vital for the security of many systems, that possible attacks on these algorithms are well studied. Understanding attacks enables implementations that resist side-channel attacks and allows for the design of appropriate countermeasures.

Research topics:

- Side-channel analysis of Neural Network implementations

- Side-channel analysis of Post-quantum cryptography

- Countermeasures against side-channel attacks

Course Offered:

Selected Publications

Probst, Matthias and Tebelmann, Lars and Wettermann, Moritz and Pehl, Michael: Remote side-channel analysis of the loop PUF using a TDC-based voltage sensor. Journal of Cryptographic Engineering 15 (1), 2025, 1 [mehr…]

Probst, Matthias and Brosch, Manuel and Gruber, Michael and Sigl, Georg: DOMREP II. 2024 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), 2024Washington DC, USA [mehr…]

Probst, Matthias and Brosch, Manuel and Sigl, Georg: Side-Channel Analysis of Integrate-and-Fire Neurons Within Spiking Neural Networks. IEEE Transactions on Circuits and Systems I: Regular Papers, 2024, 1-13 [mehr…]

Brosch, Manuel and Probst, Matthias and Glaser, Matthias and Sigl, Georg: A Masked Hardware Accelerator for Feed-Forward Neural Networks With Fixed-Point Arithmetic. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2023, 1-14 [mehr…]

Brosch, Manuel and Probst, Matthias and Sigl, Georg: Counteract Side-Channel Analysis of Neural Networks by Shuffling. 2022 Design, Automation & Test in Europe Conference & Exhibition (DATE), IEEE, 2022Antwerp, Belgium [mehr…]

Virtual Lab Tour

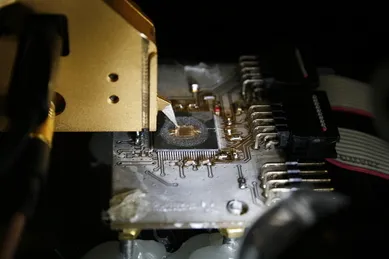

Welcome to the chair's virtual lab tour. Feel free to explore our side-channel and fault analysis lab and discover some demo videos.

Mehr Informationen