Electronic System Level (ESL)

Group Leader: Daniel Mueller-Gritschneder

Researchers: Marcel Mettler, Yu-Kai Chuang, Uzair Sharif, Rafael Stahl, Yasamin Moradi, Conrad Foik

Extreme Edge AI: Execution of Machine Learning Workloads on MCUs / IoT Nodes

A new research direction of our group is to investigate how to run Artificial Neural Network(ANN) workloads for deep learning edge application such as Keyword recognition efficiently on Low-power IoT devices at the extreme edge. These devices are usually highly resource constrained, e.g. based on Micro-Controller Units (MCUs), which only have very limited memory and computing resources.

Current research directions

- Distributed Inference: Here we investigate methods to partition Neural Networks such that they can be executed in a distributed fashion on a network of IoT nodes.

- Offline Execution-Planning and code generation: Here we investigate methods to generate, e.g., from TensorFlow Lite, and optimize the embedded software offline to minimize memory and performance overheads for inference on extreme edge devices.

Runtime Verification

Traditional verification methods such as testing and model checking do not scale with the complexity of today’s embedded systems. This problem is addressed by runtime verification which verifies the execution behavior of a system against a set of runtime requirements. In this process, the system of interest is instrumented to extract events of the system. This trace of events is then analyzed by a runtime monitor, which infers a positive verdict while the trace fulfills all runtime requirements and a negative verdict once a requirement is violated. Application areas for RV are testing and debugging before deployment, and fault recovery, reliability and safety after deployment.

Current Research Directions

- Hardware-based Monitoring Approaches: We investigate scalable monitoring architectures in HW for tile-based systems.

- Emulation of ASIC Sensors for FPGA Prototypes: We emulate ASIC power, temperature and aging sensors, which enable the prototyping of system managers on FPGAs.

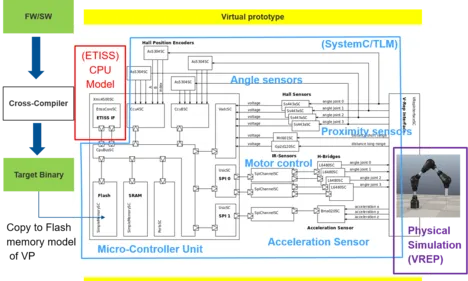

Virtual Prototypes for Embedded SW Development and Safety Evaluation

The ever increasing integration scale and architecture complexity of embedded systems and SoCs challenge today's simulation and verification methods. This lead to the shift towards Virtual Prototypes and Platforms (VPs). VPs are abstract computer models of the system, embedded electronics and its environment used for Electronic System Level Design (ESL).

In the context of our work VPs are detailed enough to emulate the embedded target software. They can work as platforms for architecture exploration, early software development and system-level verification.

VPs ascend to higher abstraction level than the conventional Register Transfer Level (RTL) for higher simulation performance. Transaction Level Modeling (TLM) using SystemC is a very, if not the most, widely adopted methodology for this purpose. In TLM, communication between modules is abstracted as transaction. Transactions are evoked by (non-clocked) events and realized by function calls.

Current research directions

- Test-driven development using virtual prototypes: We investigate how virtual prototypes can be leveraged for test-driven development of hardware-near software/firmware.

- Extendable Dynamic Binary Translation: We developed the Extendable Translating Instruction Set Simulator (ETISS). It is based on Dynamic Binary Translation (DBT) using C-Language as Intermediate Format. ETISS introduced a Plugin-mechanisms that allows to quickly insert new functionality (timing, power profiling, tracing) without need to hack the simulation loop. ETISS is an open source project.

- Automatic Generation of Firmware Safety Mechanisms: In this projet we target to generate automatic software safety mechanisms for firmware codes.

Past projects

- Early Functional Safety Evaluation by VP-level Error Injection: In safety-critical applications such as human-robot interaction or assisted and autonomous driving, the system must preserve a safe state even in the presence of HW faults. HW faults in the embedded electronics may be caused by particle strikes onto the integrated curcuits (ICs) due to radiation, IC aging or supply voltage drops. In order to develop future complex systems for safety critical applications, we investigate methods for early evaluation of the safety concepts. We use VPs and VP-level fault injection with focus on CPUs and Firmware safety mechanisms.

- Host-compiled Simulation: For TLM simulation of SoCs, the emulation of the target SW code can quickly become the performance bottleneck. TUM EDA researches CPU models that can simulate target code siginficantly faster than conventional CPU models. For this we investigate so called host-compiled SW simulation, which compiles the SW directly for the simulation host. Here we developed an annotation tool to recover the timing information of the target SW for ultra-fast but timing-accurate simulation.

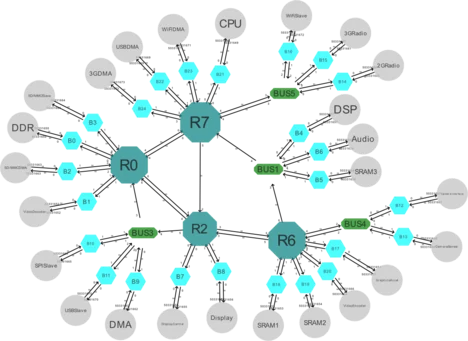

Design Space Exploration of Application-specific Networks-on-Chip (NoCs)

Rising complexity of modern SoCs leads to increasing communication between the cores. Networks-on-chip (NoCs) have been proposed as new communication architecture because they are expected to scale better with the increasing communication demands.

If the application is known at design time, custom SoC chips also require a custom appplication-specific NoC structure. In this project, Design Space Exploration (DSE) methods are investigated that find NoC stuctures, which feature an optimal compromise between area, power and latencies.

Research directions

Applying Machine Learning for Design Space Exploration: In this project we are using methods from the field of machine learning such as graph grammars, Monte Carlo Tree Search and Deep Learning techniques to efficiently explore the design space of application-specific NoCs.